### **RESPONSE TO REQUEST FOR INFORMATION**

Department of Commerce

National Institute of Standards and Technology

Submitted via: <u>MfgRFI@nist.gov</u>

In response to:

Request for Information: Manufacturing USA Semiconductor Institutes

Agency/ Docket No. 221004-0210

## Submitted by:

SRC Manufacturing Consortium (SRC.org)

4819 Emperor Blvd.

Durham, NC 27703

Point of Contact: <u>David.Henshall@SRC.org</u>

Submission Date: December 12, 2022

#### **SRC Manufacturing Consortium List of Contributors**

Jim Wieser, Texas Instruments Kristin Bennett, KB Science Tim Chainer, IBM Scott Boyce, KB Science Raja Swaminathan, AMD Karen Di Spigna, SRC Henning Braunisch, Intel Corporation Jacqueline Hall, SRC Kanad Ghose, SUNY Binghamton David Henshall, SRC Bahgat Sammakia, SUNY Binghamton John Oakley, SRC Carol Handwerker, Purdue University Marcus Pan, SRC Ganesh Subbarayan, Purdue University Todd Younkin, SRC Victor Zhirnov, SRC

With additional contributions from Analog Devices Inc., Georgia Institute of Technology, MediaTek Inc., Micron Technologies, MITRE Engenuity, NXP Semiconductors N.V., Samsung Electronics Co., SEMI Foundation, Semiconductor Industry Association (SIA), and Tokyo Electron Ltd. (TEL)

**About SRC (Semiconductor Research Corporation, SRC.org):** Established 40 years ago, SRC is a non-profit public-private partnership for semiconductor research consisting of 27 industry members, 3 government agencies, and over 100 universities. Together, they have created the technologies and trained the workforce to support the semiconductor industry with over \$2B of sponsored research.

## **Summary**

The CHIPS Act is making history. The passage of the CHIPS Act is both a great opportunity to accelerate the US semiconductor industry and also a great responsibility to ensure that the funding is used wisely to address the opportunities defined by both NIST and Congress. This is a once in a generation opportunity to redirect and propel the industry and we must get it right.

Semiconductor Research Corporation (SRC), on behalf of our industry members and academic partners, is pleased to submit this response to NIST's Microelectronics Manufacturing USA Institute (MMI) RFI. To effectively create and operate an MMI aligned with the goals of the RFI and to strengthen the Microelectronics and Advanced Technology Packaging (MAPT) innovation ecosystem including materials, design, fabrication, advanced test, assembly, and packaging capability, the Institute must manage R&D programs that effectively create technology that enables US manufacturing in the years to come. This requires successful technology

"Getting the R&D infrastructure right will determine our success for decades."

-Commerce Secretary Gina Raimondo, Industrial Advisory Committee meeting Dec. 8, 2022, Washington D.C.

generation and its transfer into industry as well as scaling education and workforce development (EWD) programs to provide skilled candidates to fill tens of thousands of US semiconductor engineering jobs in next 5-10 years.

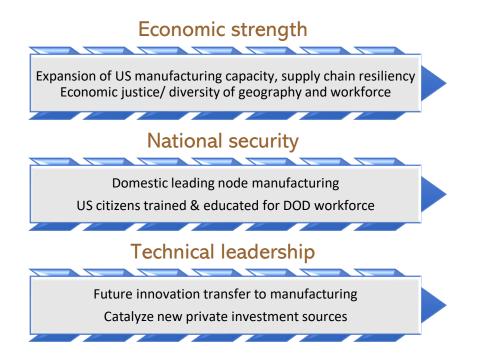

The US Semiconductor industry faces unique challenges: low (11%) global semiconductor fabrication capacity, weak (3%) global packaging capacity, and no advanced node (5 nm and below) on-shore fabrication facilities. In this RFI response, SRC and our partners have identified and described recommendations for creating and operating an MMI to help solve these problems and to "Connect people, ideas, and technology to:

- Solve industry-relevant advanced manufacturing challenges

- Enhance industrial competitiveness and economic growth

- Strengthen our national security<sup>1</sup>"

<sup>&</sup>lt;sup>1</sup> Dr. Kelley Rogers, NIST, Manufacturing USA Semiconductor Institute Request for Information Webinar October 20, 2022

## **Key Points Summary**

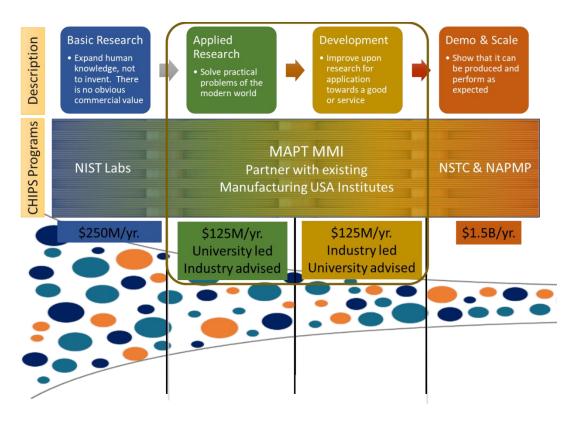

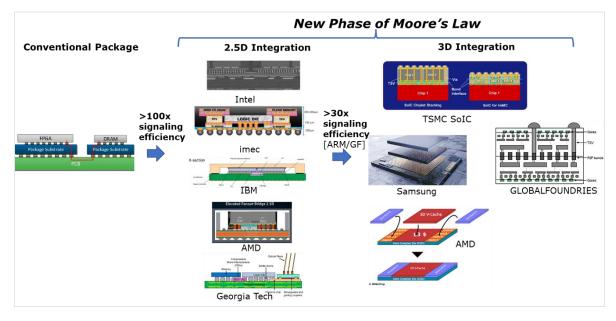

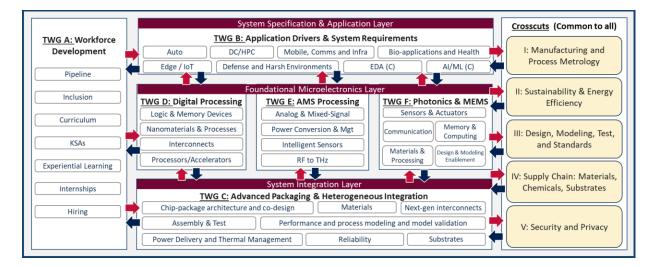

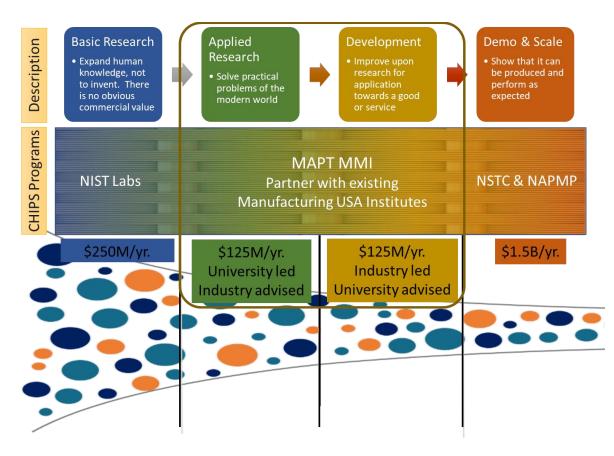

- 1) CHIPS Act R&D programs must create new capabilities that are designed concurrently to ensure a sustainable ecosystem is established for the entire innovation pipeline. (Figure 1)

- a) Technology must have a pathway to span from Basic Research through Demo & Scale to reach technology transition and deployment without falling into Valleys of Death

- b) The impact of CHIPS R&D will be maximized when R&D programs across government are designed to integrate. The MAPT Institute should create technology that feeds explicitly and intentionally into NSTC, NAPMP, NIST Metrology, DOD Commons, and existing R&D programs

- c) Grow existing infrastructure by scaling effective models and filling existing gaps

- 2) The MAPT Institute must be a convening epicenter governed by a transparent and inclusive membership model with broad membership for collaborative, high impact R&D and workforce development, prioritizing public interests including:

- a) all aspects of the supply chain from materials suppliers through systems integrators

- b) industry, academia, government, trade organizations, and beyond

- c) domestic and international companies from start-ups through industry titans, both domestically and from like-minded nations supporting US manufacturing

- d) a distributed network of higher education that spans vocational/ trade schools and community colleges through tier 1 research universities, minority serving institutions, underserved communities, veteran training, reskill/upskilling.

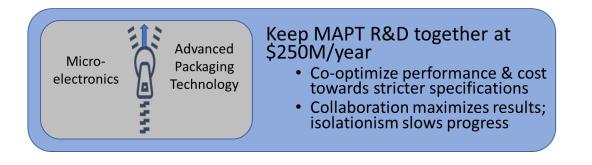

- 3) Institute technical direction and scope should be industry led, and therefore Microelectronics and Advanced Packaging Technology (MAPT) must be kept together within one institute.

- a) Complementary R&D of MAPT topics will maximize system performance, cost, and commercial relevance

- b) Unification the community, industry, and academia for maximizing impact

- c) Provides value to the community such that it can be perpetually supported without extensive government resources

- 4) The MAPT scope requires the resources of a super-sized Institute.

- a) The breadth and scope of a MAPT institute requires at least \$250M/year total, including cost-match

- b) MMI should allocate most financial resources to performing R&D, education and workforce development, and technology transfer with few financial resources used for overhead or management fees. Overhead rates should be capped at 10%.

- c) A super-size institute's risk should be mitigated by scaling existing R&D models that work effectively instead of creating a new model

*Figure 1. Microelectronics and Advanced Packaging Technology (MAPT) as a topic for a Microelectronics Manufacturing USA Institute (MMI) to bridge the Lab-to-Fab gap vision*

## Section 1 - Institute Scope

**Q1.** The Manufacturing USA semiconductor institute program is one component of an \$11 billion R&D effort that includes the National Advanced Packaging Manufacturing Program, the National Semiconductor Technology Research Center and the NIST laboratories. The entire R&D program is intended to be interconnected and comprehensive, with no gaps and minimal redundancy, to position the United States for technology and workforce leadership in the semiconductor and microelectronics sector for the long-term prosperity of the nation. Additionally, the Manufacturing USA authorizing statute specifies that new institutes must not substantially duplicate the technology focus of any other Manufacturing USA institute. From your perspective, what role do you envision for new Manufacturing USA semiconductor institutes that will best complement the other R&D investments and remain consistent with the programmatic purposes of Manufacturing USA? Since the Secretary of Commerce may award financial assistance to any existing Manufacturing USA institutes for work relating to semiconductor manufacturing, what role do you envision for existing, federally sponsored Manufacturing USA institutes with respect to semiconductor manufacturing?

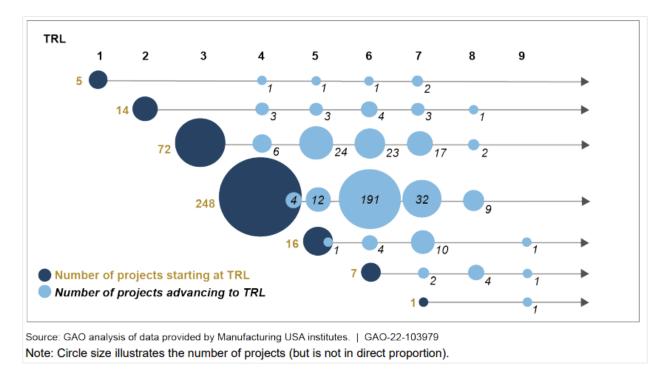

The different R&D programs envisioned under the CHIPS Act should together enable a semiconductor ecosystem for a vibrant lab-to-fab transition. Historically, the Manufacturing USA Institutes (M-USA) have been effective by starting projects at the "lab" end of the spectrum and delivering to the "fab" end; most M-USA projects have started at Technology Readiness Levels 3 or 4<sup>2</sup> as shown in **Figure 2**Error! Reference source not found.. However, since tools for "upstream" activities of chip-package co-design are not readily available, more integration at lower TRLs is necessary for semiconductors. Given this, and given the plans for NSTC and NAPMP, the newly formed M-USAs for semiconductors will be most effective starting at TRLs 2-4 beginning with design/simulation, then transitioning to TRLs 4-5, short of building a prototype system but feeding explicitly and directly into other CHIPS Act R&D programs such as NSTC and NAPMP.

<sup>&</sup>lt;sup>2</sup> www.gao.gov/assets/gao-22-103979-highlights.pdf

The role for existing federally sponsored Manufacturing USA institutes would be to directly collaborate with the new Microelectronics Manufacturing USA Institutes (MMI) through joint R&D projects and workforce development programs and inform the new MMI's as they remain focused more specifically on mainstream semiconductor manufacturing (including microelectronics and advanced packaging technology). The current Manufacturing USA institutes that are most related to semiconductor manufacturing include AIM Photonics (for integrated photonics), NextFlex (for flexible electronics) and Power America (for power electronics using wide bandgap semiconductors). We also suggest CESMII (Smart Manufacturing) and ARM (robotics) as cross-cutting institutes. Each of the existing institutes address important topics of emerging microelectronic components and applications, however, they do not directly focus on mainstream developments in semiconductor manufacturing.

In support of collaboration, we recommend that some of the CHIPS Act funding should go to existing manufacturing institutes and dedicated to collaboration with the possible institute(s) established from this RFI. Collaborations could include governance where leaders from existing institutes participate on boards of the new institute(s), in road mapping activities, on proposals and projects, on joint EWD activities, or in joint technology transfers to NSTC and NAPMP.

**Q2.** The technological breadth of innovation in semiconductors and microelectronics is likely larger than can be served by any single Manufacturing USA institute. Therefore, each Manufacturing USA semiconductor institute should have an appropriate scope to ensure that each institute is impactful and does not duplicate efforts of other programs. Historically, institutes in the current network of existing Manufacturing USA institutes have generally been funded for an initial 5 years at \$150 million to \$600 million, including federal funding and cost-sharing (co-investment) from non-federal partners. What would be the ideal scope and corresponding financial investment from federal and non-federal partners, for a Manufacturing USA semiconductor institute to achieve the needed impact on competitiveness?

Given the need for global competitiveness and onshoring capacity, and to ensure that the new Manufacturing USA semiconductor institute is impactful, it is recommended that a single institute be created through a public-private partnership (PPP) that integrates both microelectronics and advanced packaging technology (MAPT) at a much higher investment level as compared to typical M-USA. To achieve the needed impact on competitiveness, the minimum requirement would be at least \$250M/year, with \$125M/year federal funding and \$125M/year non-federal cost share. We anticipate cost share will increase in subsequent years but would begin with a 1:1 ratio. Since the global semiconductor manufacturing industry revenue was \$560B in 2021<sup>3</sup> with \$1,065 billion<sup>4</sup> projected by 2030, we recommend the size of the institute follow a similar growth trajectory.

This investment has impact across multiple end markets. According to Deloitte, the chip shortage in the past two years resulted in revenue losses of more than \$500 billion worldwide between the semiconductor and its customer industries, with lost auto sales of more than \$210 billion in 2021 alone.<sup>5</sup> A new M-USA institute of an appropriate magnitude and scope would help to reverse the impact of the recent shortage and further reduce the risk of future recurrences.

Currently, high costs as well as lack of in-house talent restrict access to electronic design and analysis (EDA) tools, modeling, technology customization, metrology tools, product qualification, and reliability assessment for small and medium-sized enterprises. The above activities are critical to create an open microelectronics and advanced packaging technology lab-to-fab ecosystem in the US. However, these activities are not part of existing Manufacturing USA Institutes and therefore necessitate a broader scope and higher funding levels for the planned institutes.

<sup>&</sup>lt;sup>3</sup> www.semiconductors.org/wp-content/uploads/2022/11/SIA\_State-of-Industry-Report\_2022.pdf

$<sup>{}^4</sup> www.mckinsey.com/industries/semiconductors/our-insights/the-semiconductor-decade-a-trillion-dollar-industry} \\$

$<sup>04/\#: \</sup>because text = Latest \% 20 Updates \& text = The \% 20 chip \% 20 short age \% 20 will \% 20 cost, consultant \% 20 A lix Partners \% 20 estimated \% 20 lin \% 20 September = 100 and \% 20 an$

**Q3.** Potential technology areas of focus that could be addressed by the Manufacturing USA semiconductor institutes to complement the National Advanced Packaging Manufacturing Program and the National Semiconductor Technology Research Center in Question 1 are listed below. What are your thoughts on the appropriateness of each for the scope of work for a Manufacturing USA semiconductor institute? What other topics should be included in the scope of an institute?

- Chip-package architectures and co-design of integrated circuits and advanced packaging. May include artificial intelligence, security, test methodologies, etc.

- Technologies to increase the microelectronics manufacturing productivity of American workers, lower costs and offset the drastic shortfall of skilled workers.

- Assembly and Test metrologies to develop new analytical equipment and analysis capabilities based upon standards.

- Coding and system software with novel computing paradigms and architectures, including chiplet compatibility with earlier generations.

- Integration of security into packaging, interposers and/or substrates.

- High Density Interposers and substrates, incorporating new materials and designs.

- Chiplet-enabled trusted packaging facilities that obviate the need for trusted foundries.

- New materials, such as glass for substrates, or compound semiconductors.

- Environmental Sustainability for semiconductor manufacturing.

- Analog and Gigahertz Technology materials and metrology, enabling beyond 5G, the Industrial Internet of Things and Industry 4.0.

- Performance and Process Modeling and Metrology

The topics proposed above are highly appropriate for the scope of MMI R&D topics, however additional technical topics related to semiconductor manufacturing technology are necessary. The technical topics included within the scope of the institute(s) should be guided by the community consensus, NIST-sponsored Manufacturing and Advanced Packaging Technology (MAPT) roadmap which includes contributions from over 90 organizations within the semiconductor ecosystem. The initial reports have been provided to NIST and a preliminary public release is expected in Q1 2023.

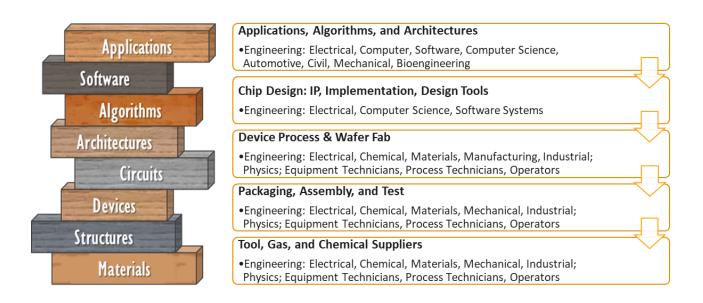

Beyond using the MAPT Roadmap as a guide, the scope of the institute should include the full stack of R&D from devices, structures, and materials through circuits, architectures, and algorithms. More specific technologies include:

- Digital Processing

- Analog/ Mixed Signal Processing

- Micro(nano)-electromechanical systems MEMS/NEMS and sensors

- Device processing and manufacturing yield estimation

- Integrating thermal solutions with chip stacks

- Reliability assessment of complex semiconductor devices and advanced microelectronic packages

- Chiplet interconnection standards

It is imperative that the new Manufacturing USA semiconductor institute integrate both microelectronic and advanced packaging topics, rather than focusing on one or several standalone technical areas. The 2030 SRC Decadal Plan for Semiconductors<sup>6</sup> describes the need for benchmarking advances needed in both microelectronics and advanced packaging technology to drive and deliver the holistic needs of systems. The critical need for such co-design and cointegration between microelectronics and advanced packaging was projected, in-part, by Gordon Moore in his famous paper, *"Cramming More Components onto Integrated Circuits"* (1965), which forms the basis of "Moore's Law." He states that "The total cost of making a particular system function must be minimized ... [at some point] *It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected*. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically." He refers to this as the "day of reckoning."

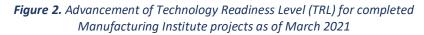

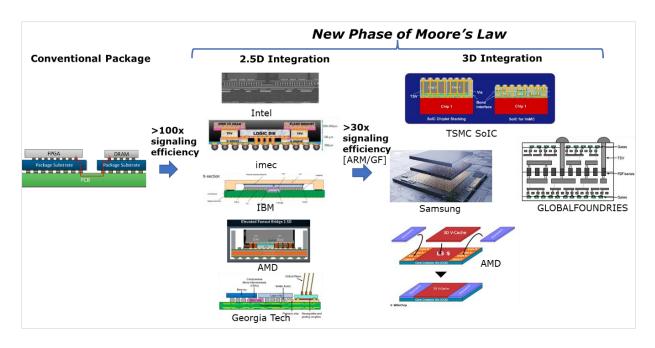

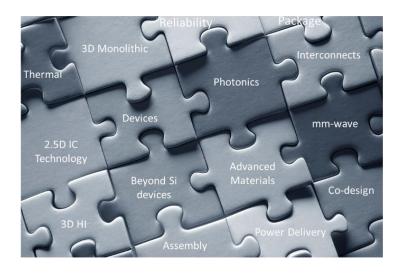

Today, the 'day of reckoning' has arrived and there is no critical mass in the US in this new era of Moore's Law – this is a key opportunity for the new Manufacturing USA semiconductor institute. Where monolithic integration forms all circuit functions on a single common semiconductor (at the wafer scale), heterogenous integration enables the concatenation of 'chiplets' of various functionalities (logic, I/O, memory, power conversion, passives, photonics, mm-wave, etc.) and materials in a manner that mimics/exceeds monolithic-like performance and utilizes advanced off-chip '2.5D' and '3D' interconnects and packaging to provide flexibility in fabrication and design, improved scalability, reduced development time, and reduced cost.

This approach is becoming accepted commercially; **Figure 3** below gives a brief snapshot of the various emerging advanced packaging concepts in this new era of Moore's Law. While these

<sup>&</sup>lt;sup>6</sup> www.src.org/about/decadal-plan/

emerging packaging technologies vary in approach, they all seek to blur the boundary between on-chip and off-chip interconnect densities for power and performance considerations and train the workforce to adopt this evolving mindset.

*Figure 3.* Snapshot of the various emerging advanced packaging concepts in the new era of Moore's Law

**Q4.** What criteria should be used to select technology focus areas in delineating the scope for a Manufacturing USA institute focused on semiconductor manufacturing?

The criteria for selecting technology focus areas must be driven by industry, especially those with significant domestic manufacturing capacity, with input from academia and government. The technology selection should be consensus-driven and be built on a foundation from existing and ongoing roadmaps. The selection criteria must also include the feasibility of the technology to impact the goals of the MMI, NIST, and the CHIPS Act, supporting a robust manufacturing infrastructure that can be sustained well beyond the 5-year target funding from government while reducing manufacturing supply chain risks. Additional criteria should include:

- Impact that the technology can have on bringing underrepresented communities and geographic regions into the industry

- TRL/MLR aligned with the M-USA institute model, which is typically 3- 5<sup>7</sup>

- Complementary to adjacent CHIPS Act programs including NSTC, NAPMP, DOD Commons, and NIST metrology

<sup>&</sup>lt;sup>7</sup> www.gao.gov/assets/gao-22-103979-highlights.pdf

- Ability to co-optimize microelectronics technology with advanced packaging technology to make the sum better than each individual

- Strong emphasis on equitable drivers for semiconductor workforce development across all levels of post-secondary education levels

**Q5.** What technology focus areas that meet the criteria suggested in Question 4 above would you be willing to co-invest in?

SRC is a crossroads of collaboration between technology companies, academia, government agencies, and other participants in the semiconductor ecosystem. With 27 member companies supporting US manufacturing, partnering with more than 100 universities and multiple government agencies, SRC manages several research programs with a combined 55 research topics and more than 500 research projects carried out by over 1,200 SRC-sponsored students annually. For the Manufacturing USA Institute, SRC and its members would co-invest in the technical topics illustrated in **Figure 4** below to ensure comprehensive R&D and impact. These topic areas are aligned with the NIST Microelectronics and Advanced Packaging Technology Roadmap (in progress), and industry is currently funding these topics through active SRC research programs now.

*Figure 4.* Suggested technology structure of a Manufacturing USA institute focused on semiconductor manufacturing by adopting learnings from NIST- sponsored MAPT Roadmap, with contributions from over 90 organizations in the semiconductor ecosystem

## Section 2: Institute Structure and Governance

**Q6.** Existing Manufacturing USA institutes were launched and operate in alignment with the design principles published in 2012 as the *National Network for Manufacturing Innovation: A Preliminary Design.* Are there any unique considerations for the semiconductor and microelectronics sector that may require modifications to the conventional design for any Manufacturing USA semiconductor institutes under consideration?

#### UNIQUENESS OF THE INDUSTRY

The semiconductor industry differs from many other manufacturing industries in four distinct ways: 1) regional specialized manufacturing, 2) societal reliance; 3) rapid innovation

#### Unique Industry

- Regional specialized manufacturing

- Societal reliance

- Rapid innovation/ highly

- technicalHigh fab investment

- necessity • Supply chain

Unique

redundency

Requirements

Collaboration

Workforce planning

cycles of high technology; and 4) extremely high manufacturing facility costs. Here is how each of these <u>four attributes</u> make the industry unique:

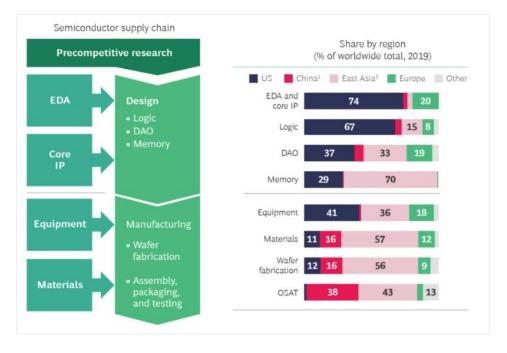

#### 1) Regional Specialized Manufacturing

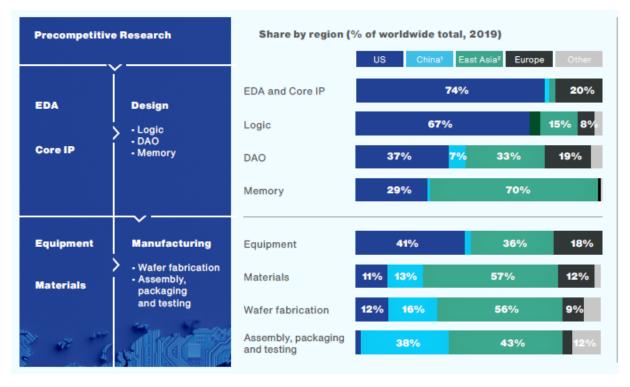

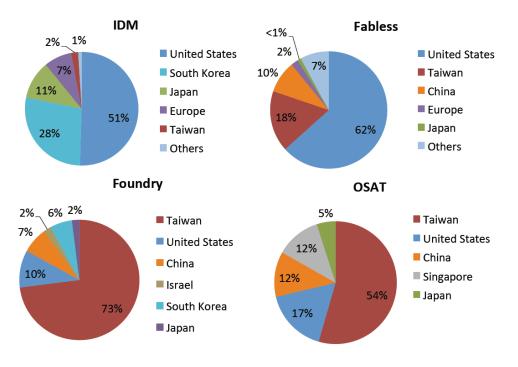

Over the past several decades, the semiconductor industry has changed the way we work, play, and connect, while enabling trillions of dollars in economic prosperity and transforming national security. However, during these decades, the industry fractured into specialized parts of the collective manufacturing process (

**Figure** *5***)**, each of which is highly sophisticated and not readily duplicated because of specialized manufacturing and IP. While each of these specializations has different economic and risk characteristics, together they deliver a system that has enabled massive industrial growth and yields a global supply chain that is highly optimized to convert silicon ingots into integrated circuits for many industries and consumer applications.

| 1950s | 1960s               | 1970s                  |   | 1980s                  | 1990s               | 2000s                  | 2010s               |

|-------|---------------------|------------------------|---|------------------------|---------------------|------------------------|---------------------|

|       |                     |                        | _ | _                      |                     |                        |                     |

|       |                     |                        |   |                        |                     |                        | Software            |

|       |                     |                        |   |                        | IP Provider         | IP Provider            | IP Provider         |

|       |                     |                        |   | Fabless Companies      | Fabless Companies   | Fabless<br>Companies   | Fabless Companies   |

|       | Manufacturing Tools | Manufacturing<br>Tools |   | Manufacturing<br>Tools | Manufacturing Tools | Manufacturing<br>Tools | Manufacturing Tools |

| IDM   | IDM                 | IDM                    |   | IDM                    | IDM                 | IDM                    | IDM                 |

|       |                     | EDA Tools              |   | EDA Tools              | EDA Tools           | EDA Tools              | EDA Tools           |

|       |                     |                        |   | Foundries              | Foundries           | Foundries              | Foundries           |

|       |                     |                        |   |                        |                     | Packaging              | Packaging           |

## *Figure 5.* Functional evolution of the Semiconductor Ecosystem (1950s-2010s) into specialized elements of the supply chain<sup>8</sup>

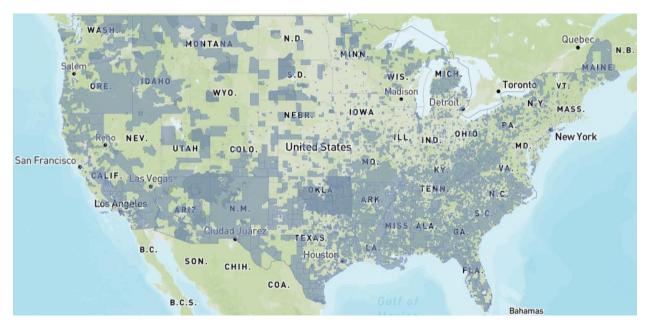

As the semiconductor industry evolved into these specialized elements, geographic regions emerged as hubs of the supply chain (Figure 6). This regional specialization has enabled global economic growth for over 40 years and the continuation of Moore's Law well beyond what a single actor, alliance, or region could have accomplished.

Figure 6. An Example of the Semiconductor Global Supply Chain and Its Specialized Regions<sup>9</sup>

Although this regional specialization enabled global economic prosperity, it has resulted in excessive risk and growing economic dependence on foreign sources, excessive risk to national security, and a lack of visibility into global demand and shortages for manufacturing (Figure 7).

<sup>&</sup>lt;sup>8</sup> www.semiconductors.org/wp-content/uploads/2018/06/SIA-Beyond-Borders-Report-FINAL-June-7.pdf

<sup>&</sup>lt;sup>9</sup> www.semiconductors.org/wp-content/uploads/2021/05/BCG-x-SIA-Strengthening-the-Global-Semiconductor-Value-Chain-April-2021\_1.pdf

*Figure 7.* Internationalization of the Semiconductor Value Chain (% of Total Revenue, 2015)<sup>10</sup>

Many vulnerabilities exist throughout the manufacturing supply chain, which amount to a critical threat to National Security. Of particular concern are the risks associated with Outsourced Semiconductor Assembly and Test (OSAT). OSAT's are an important part of the supply chain and are particularly vulnerable because they are often the last step before integration into a system. For example, bad actors can target OSAT processing by inserting trojans into packages, resulting in great risk to national security.

A new institute will create domestic advanced packaging technology (APT) R&D capabilities, leading to domestic manufacturing capabilities and a more robust and secure supply chain. This APT infrastructure needs to be tightly coupled and integrated with microelectronics to co-design between chips and packaging.

#### 2) Societal Reliance: "Chips are the foundation of the modern world"

Society relies on semiconductors. They have become essential to our quality of life whether navigating to a soccer game, communicating with loved ones, making payments, or managing workflows.

Semiconductor chips are a critical ingredient to the economy for both manufacturing and nonmanufacturing segments. As Donna Dubinsky, Senior Counselor to the Secretary for CHIPS

<sup>&</sup>lt;sup>10</sup> https://www.semiconductors.org/wp-content/uploads/2018/06/SIA-Beyond-Borders-Report-FINAL-June-7.pdf

Implementation, stated in the *CHIPS for America Incentives Program* webinar on September 29, 2022: "Chips are the foundation of the modern world." Manufacturing for most industries relies on a steady, reliable supply of trusted semiconductors. Any disruption in chip supply can have dramatic effects on manufacturing across many industries and on the economy, as was felt during the pandemic. Semiconductors are the building blocks of many other nonmanufacturing industries that cease to function without them. Examples include:

-Donna Dubinsky, CHIPS for America Incentive Program Webinar, Sept 2022

- Automotive

- Banking and finance

- National infrastructure spanning GPS, the power grid, communications and data networks, transportation networks, etc.

- Aerospace, Defense, and weapons systems

- Healthcare

#### 3) Rapid Innovation/ Highly Technical

The technical capabilities of the semiconductor industry are unmatched. Moore's Law has provided the industry with a steady cadence of performance gains such that the number of transistors on a chip has doubled every two years for about half a century. Further, the number of transistors manufactured is staggering at a cumulative total of 13 sextillion (1.3×10<sup>22</sup>) manufactured worldwide between 1960 and 2018<sup>11</sup>. That is roughly one transistor for every grain of sand on earth. Some transistors are just a few atoms wide, while the range of power management for transistors varies from nano-watts to kilowatts. This technology and innovation are only possible because of the high R&D intensity (R&D expenditures/Revenue) throughout the industry. The only industry that surpasses semiconductor R&D intensity is Pharma & Biotech<sup>12</sup>.

#### 4) High cost of capital expenditures for manufacturing

Manufacturing semiconductors is a high capital expenditure (capex) endeavor because of the high cost of specialized equipment and the cost of controlled environment requirements in which to

<sup>&</sup>lt;sup>11</sup> https://computerhistory.org/blog/13-sextillion-counting-the-long-winding-road-to-the-most-frequently-manufactured-human-artifact-in-history/?key=13-sextillioncounting-the-long-winding-road-to-the-most-frequently-manufactured-human-artifact-in-history <sup>12</sup> www.semiconductors.org/wp-content/uploads/2022/11/SIA\_state-of-Industry-Report\_2022.pdf

manufacture chips. Typically, the industry spends about 20% of revenue on capex, with construction of a single fabrication facility costing up to \$20B<sup>13</sup>.

#### SPECIAL CONSIDERATIONS

Due to the unique attributes mentioned above, there are primarily <u>3 special considerations</u> for creating and operating a Microelectronics Manufacturing USA Institute (MMI). These include: 1) the necessity to collaborate, 2) the need for supply chain redundancies, and 3) considerations for workforce development planning. Each of these is discussed in the following three sections:

#### 1) Collaboration Necessity

There will be a large number of participants, partners, and members all working together. Critical collaboration would need to happen between all of the CHIPS Act R&D programs including NIST Metrology, MMI, NSTC, and NAPMP, as well as the Workforce and Education Fund, the DOD Commons, and the International Technology Security fund. Only by working together can the objectives of CHIPS Act be met. Designing and creating these programs and corresponding PPP's accordingly will ensure no gaps with minimal overlaps, and best leverage the funds provided by Congress to build a complete innovation pipeline with seamless integration. This will also be important to avoid market failure between Proof of Concepts created in government and university labs, and the development, scaling, and manufacturing capabilities of the industry.

It is highly important for the MMI to interact with other Manufacturing USA institutes within the network, and preferably collaborate across institutes on research topics. Not only would this strengthen the performance of both institutes, but it would enhance the performance of the M-USA network.

Collaboration between different scientific disciplines is also needed. Interdisciplinary collaboration across many technical fields such as Materials Science, Physics, Electrical Engineering, Mechanical Engineering, Chemistry, Computer Science, and more have been the requisite recipe for innovation success in the industry and must be continued through this institute.

#### International Collaboration

The institute will need to include international partners from the US and ally countries for any comprehensive solution, thereby creating "democracy chips" (chips manufactured in democratic countries) to ensure global resources are contributing to the CHIPS Act objectives. This can be a

$<sup>^{13}</sup> www.semiconductors.org/wp-content/uploads/2020/09/Government-Incentives-and-US-Competitiveness-in-Semiconductor-Manufacturing-Sep-2020.pdf$

challenge because, as an international industry, countries that are otherwise adversaries rely on one another to support their respective economies.

For example, China is often perceived as a political adversary of the US. Yet China relies on sourcing semiconductors designed in the US and produced in Taiwan. The US, and our global society at large, are dependent on China to turn those semiconductors into finished products. For security reasons, it is important that the US does not sell state-of-the-art semiconductors to China that could potentially be integrated into weapons systems used against the US and allies.

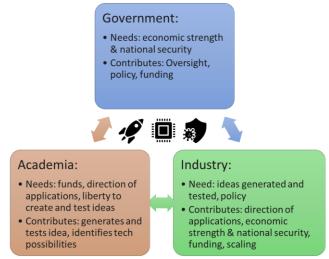

#### Industry - Academia - Government Collaboration

The US, along with like-minded nations, have demonstrated the ability to achieve monumental results when government, industry, and academia work together. Historical examples of these monumental achievements include the development and widespread use of vaccines, the first moon landing, and the creation of the semiconductor industry and internet. In order to achieve success on a similar scale in the semiconductor industry, each of those three entities must play a unique role to ensure the relationship is symbiotic:

a) **Government** should initiate creation of the institute, but not be the dominant sponsor in perpetuity. Instead, government sponsorship should diminish after the start-up period. If the institute cannot operate primarily through industry sponsorship, then it is not properly serving the community. Although the government should

not generally engage in long-term research agendas, signals of long-term support should be provided by government to ensure industry participation. Government should financially support risk that is too high for industry to pay for alone. Government needs to convince companies investing in the institute that these companies' commitments of human and financial capital will not be abandoned by their government partners in a few years.

b) *Industry* should lead the technical direction of the institute because they provide critical knowledge about what technologies the markets will support and what

technologies can be scaled. This position allows industry to best determine which technologies should advance throughout the innovation pipeline. They also provide important insight into past commercial failures - the details of which may not be known to government or academia.

c) *Academia* should be the driving force for creating and testing new technologies that will be matured through the innovation pipeline. Their liberty to create and test new ideas without the burden of meeting quarterly financials must be protected, allowing them to explore new vectors, understand the fundamentals of new innovations, and find new pathways. Further, it will be academia that leads the effort of workforce development.

#### 2) Supply Chain Redundancy and Resiliency is needed

Without a complete supply chain, domestic manufacturers are susceptible to failures of which the US is not in control. The global supply chain has historically provided US companies with access to the latest technologies at fair cost and reliable delivery. However, there are increasing risks posed by geopolitical conflict, dramatic weather events, regional economic instabilities, and, most recently, pandemics. These risks threaten the supply chain's stability, and in turn, US economic and national security. Specifically, although US IDM and Fabless/Design companies account for over 50% of the revenue in the semiconductor industry, much of the manufacturing capacity is overseas. This has led to a reduction in US manufacturing capacity from 37% in 1990 to 12% in 2020. Countering this, Samsung and TSMC's growing commitment to building semiconductor manufacturing facilities in the US is a welcomed source of stability.

Each link of the semiconductor supply chain has few participants in niche areas. These are often defined by companies or by regions. For example, ASML dominates lithography equipment; design software is dominated by 3 companies; OSAT is dominated in SE Asia. This creates narrow pinch points throughout the supply chain.

When designing solutions for the domestic semiconductor industry to address supply chain risk mitigation, it is important to have some domestic capability for every step of the supply chain. Unlike other industries that can trade one material or component for another (although sometimes at higher cost) and still function correctly, the semiconductor industry is highly specialized resulting in few to no alternatives to serve as reinforcements of the supply chain.

To further reduce supply chain manufacturing risk in an economical way, the institute should identify adjacent industries that have manufacturing capabilities that can be repurposed with low

barriers to support the semiconductor industry if the supply of critical materials is jeopardized. This is especially true for chemicals and materials, which are generally agnostic to the end application, as compared to integrated systems which are more specific to the end application. For example, the robust US chemical industry could support the semiconductor industry by repurposing resources towards semiconductor-specific needs in the event of an international semiconductor supply chain crisis.

#### 3) Workforce planning is needed

There are **four main areas** that must be considered in order to bolster the semiconductor workforce: 1) education and training, 2) geographic challenges, 3) diversity and inclusion, and 4) talent attraction.

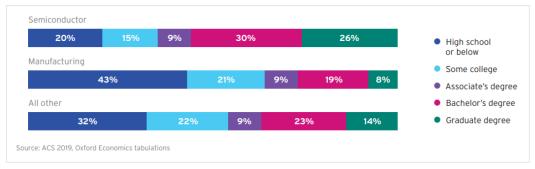

**Education and Training** - The semiconductor workforce is unique in that it requires extensive use of MS and PhD educated workers that support the high R&D intensity to develop, support, and optimize the next generation of manufacturing. Compared to other manufacturing, the semiconductor industry relies on a workforce with about twice as many bachelor's degrees and advanced degrees (Figure 8). To support this, access and retention of both US and foreign-born talent is critical to the industry's workforce needs<sup>14</sup>.

Figure 8. Educational attainment in the semiconductor industry

**Geographic Challenges** - Equipment operators and technicians with specialty skills and training are also critical to the industry. In general, these technicians look for work in factories located in the same region in which they completed training and do not tend to relocate. Conversely, semiconductor manufacturing workforce with graduate degrees are more apt to move to a different region or even a different country to find work.

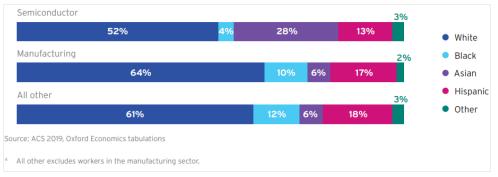

**Diversity and Inclusion** - Historically, the semiconductor industry represents a homogenous workforce of predominantly men that are Asian and Caucasian (Figure 9), where men make up 75-

$<sup>^{14}</sup>$  www.semiconductors.org/wp-content/uploads/2021/05/SIA-Impact\_May2021-FINAL-May-19-2021\_2.pdf

90% of the industry workforce<sup>15</sup>. A truly resilient workforce needs to be diverse and inclusive of all ideas and capabilities, including underrepresented communities.

Figure 9. Race and ethnicity profile

**Talent attraction:** To supply enough workers for the industry there must be programs to attract High School graduates into the field. This could require a span of approaches including engineering competitions, hands-on workshops, 'educating the influencers' programs for High School math and science teachers as well as guidance counselors, and engineering career days.

**Q7.** Semiconductor R&D and manufacturing cover substantial technical breadth.

- A) What business models or best practices should be employed by a Manufacturing USA semiconductor institute to support U.S. leadership and effectively manage emerging technologies to support commercialization?

- B) What advantages or disadvantages would there be to one "super-sized" Manufacturing USA semiconductor institute that would cover the technology sector broadly?

- C) Since Congress authorized the NIST Director to establish up to three institutes, what advantages or disadvantages would there be for multiple Manufacturing USA semiconductor institutes each with a smaller scope focused on a specific technology area?

- D) How would one Manufacturing USA semiconductor institute or multiple institutes structure relationships with other significant partners to spur collaborative work?

#### A) Business models and best practices

We acknowledge the excellent best practices and review work performed as required by the Revitalize American Manufacturing and Innovation (RAMI) Act of 2014. Manufacturing USA was created to improve the competitiveness of US manufacturing by accelerating innovation and implementation of advanced manufacturing capabilities. Each institute creates the necessary

<sup>&</sup>lt;sup>15</sup> www.gsaglobal.org/wp-content/uploads/2020/05/BRIEF-GSA-Women-in-the-Semiconductor-Industry-Survey-Results-2019.pdf

focus and provides the state-of-the-art facilities needed to allow collaborative, pre-competitive development of promising technologies. An institute provides workforce education and training in advanced manufacturing. It also promotes the creation of a stable and sustainable innovation ecosystem for advanced manufacturing. We also acknowledge the National Academies report "Manufacturing USA Revisited: Securing Advanced Manufacturing in the United States - A Workshop.<sup>16</sup>"

While reading these reports and leveraging SRC and other collaboration models, we recommend the following attributes be included in an MMI governance and business model:

- 1) The organizations creating, operating, and managing the institute should have the authority to make timely decisions, yet still be accountable and transparent.

- 2) The institute must be flexible and adaptable to incorporate new insights for optimization. That is, as the organization begins to operate, there will be new realizations of what works and what does not. It will be important to incorporate these findings to refine the operational model.

- 3) The institute must require rotation of leadership to welcome fresh perspectives from organizations and activate the larger community. For example, Board of Directors chair, Technology Advisory Board chair, Government Advisory Board, etc.

- 4) The institute must produce specific, measurable, short- and long-term goals with accountability to a management oversight board to ensure performance. To support this, the governance must:

- a) Be a trusted, credible, guide for the industry

- b) Use transparency, data-driven decisions, and consensus

- c) Drive collaboration, consensus, and cooperation as imperatives

- d) Operate under and OTA authority with government

- 5) The institute must focus on collaboratively funded R&D. This was discussed extensively in the response to Question 6.

- a) User facilities that are available to all members and mapped to their interests

- b) IP structures that enable collaboration and investment

- i) Share IP so partners can collaborate together

- ii) Protected/ limited access IP allows for greater financial investments by industry members

- iii) Encourage inclusion and protection of background IP

$<sup>^{16}</sup> www.nationalacademies.org/our-work/manufacturing-usa-securing-advanced-manufacturing-in-the-united-states-a-workshop and the states are stated as a securing advanced and the stated as a securing advanced as a securing adva$

- 6) The institute must include of all parts of the ecosystem, including:

- a) all aspects of supply chain from materials suppliers through systems integrators

- b) industry, academia, government, trade organizations, etc.

- c) start-ups through industry titans from the US and like-minded nations

- d) US higher education from trade schools and community colleges through tier 1 research universities, minority-serving institutions, veteran training, reskill/ upskilling; geographic diversity and underserved communities

- e) span the full stack from materials through packaging, applications, and hardware/ software codesign

#### Technology Transfer

Critical to meeting the objectives of the CHIPS Act strategy and the M-USA institute(s) is the need to ensure technology transfers from research, through the innovation pipeline, to manufacturing using a stage-gate methodology to increasingly invest in maturing the most promising technologies. Developing technology but not transferring it to industry can be an enormous missed opportunity for supporting national interests. As such, the institute must use best practices for ensuring that technologies become useful. To do this, a full portfolio of approaches must be used across different levels of technology maturity and technology type (materials, design, software, etc.) to ensure it remains on a path to market. Several methods have proven highly effective such as DARPA's Embedded Entrepreneurship Initiative and SRC's industry liaisons.

Start-ups can be a rich resource for transferring technology into manufacturing. To benefit from this the institute should support concepts employed by Silicon Catalyst and transition them into a national resource available at the Institute.

The broad goal of this innovation pipeline is to create new technology, mature that technology, and manufacture it to strengthen the US economy, national security, and society as a whole. Here are three examples of how the technology pipeline - from academic labs to manufacturing - would work. We recommend that each of these be pursued in appropriate proportions:

- 1) Transfer technology from the institute directly into commercial members using best practices that are proven to work as mentioned above.

- 2) Transfer technology from the institute to prototyping and development facilities, such as the Coalitions of Excellence (COE's) associated with the NSTC and/or NAPMP for maturation before transferring into industry.

3) Transfer technology from the institute to start-ups for maturation and ultimately for manufacturing, either directly by the startup or through acquisition of the start-up by a manufacturing company.

#### General best practices

To support the financial needs of the MMI, and following along with others' best practices, it will be helpful to allow the institute to support privately funded initiatives using institute resources for a fee.

#### B) Advantages of a super-sized MMI

#### [Note: some portions of this response are restated from Question 3 responses]

It is imperative that the new Manufacturing USA microelectronics institute integrate both microelectronic and advanced packaging topics, rather than focusing on one or several standalone technical areas. The 2030 SRC Decadal Plan for Semiconductors<sup>17</sup> describes the need for benchmarking advances needed in both microelectronics and advanced packaging technology to drive and deliver the holistic needs of systems. Further, the critical need for such co-design and co-integration between microelectronics and advanced packaging was projected, in-part, by Gordon Moore in his famous paper, *"Cramming More Components onto Integrated Circuit"* (1965), which forms the basis of "Moore's Law." He states that "The total cost of making a particular system function must be minimized ... [at some point] *It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected*. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically." He refers to this as the "day of reckoning."

Today, the 'day of reckoning' has arrived and there is no critical mass in the US in this new era of Moore's Law – this is a key opportunity for the new Manufacturing USA semiconductor institute. Where monolithic integration forms all circuit functions on a single common semiconductor (at the wafer scale), heterogenous integration enables the concatenation of 'chiplets' of various functionalities (logic, I/O, memory, power conversion, passives, photonics, mm-wave, etc.) and materials in a manner that mimics/exceeds monolithic-like performance and utilizing advanced off-chip '2.5D' and '3D' interconnects and packaging to provide flexibility in fabrication and design, improved scalability, reduced development time, and reduced cost.

<sup>&</sup>lt;sup>17</sup> www.src.org/about/decadal-plan/

This approach is becoming accepted commercially; **Figure 10** below gives a brief snapshot of the various emerging advanced packaging concepts in this new era of Moore's Law. While these emerging packaging technologies vary in approach, they all seek to blur the boundary between on-chip and off-chip interconnect densities for power and performance considerations. As such, it is critical that the new Manufacturing USA semiconductor institute combines microelectronics and advanced packaging.

Figure 10. Snapshot of the various emerging advanced packaging concepts in the new era of Moore's Law

Given the magnitude of the industry and global impact needed and the breadth of technologies, we recommend one 'super-sized' institute that covers technical areas associated with Microelectronics and Advanced Packaging Technology (MAPT) along with a possible second, and separate, independent institute, which is of standard size, covering technical areas of Virtualization, Visualization, and Automation (VVA) especially for fab construction and operation.

Creating and operating a super-sized MMI based on MAPT would advance research and commercialization of semiconductor manufacturing technology more competitively, thereby have a direct impact on:

One Super-Sized institute to build domestic multi-dimensional Microelectronics and Advanced Packaging Technology (MAPT) Infrastructure: The US microelectronics infrastructure excels at basic, and early-stage applied research. While this is true for microelectronics, there is a limited infrastructure for advanced packaging technology R&D domestically, including 2.5/3D stacking, heterogeneous integration, chiplet design, etc. We recommend that the institute include the continuation of nurturing the semiconductor infrastructure for R&D while building the R&D infrastructure for Advanced Packaging Technologies 10-100X larger than it is today. As 2D geometric scaling runs out of atoms for transistors in the coming years, the next wave of cost/performance gains will come from 3D integrated circuits (3DIC) through both monolithic and heterogeneous integration with increased reliance on advanced packaging technologies. These technologies will drive the continuation of Moore's Law technology and economic advancements in the coming years. Since no country currently has an extensive advantage in this 3DIC field, the opportunity is ripe for the US to take leadership and reap the rewards in the following decade for Microelectronics and Advanced Packaging Technology (MAPT).

**Figure 11.** Microelectronics and Advanced Packaging Technology (MAPT) as a topic for a Microelectronics Manufacturing USA Institute (MMI) to bridge the Lab-to-Fab gap vision

Furthermore, the institute needs a multi-dimensional plan which includes a robust supply of technologies and ideas that can align with, and feed into, the NSTC and the NAPMP (Figure 11). This comprehensive plan from Basic Research through Demo & Scale as outlined above must include several factors and infrastructure for:

- Technologies that mature across the Technology Readiness Level (TRL) scale. This includes moving from Basic Research to Applied Research to Development and into Demo and Scale by designing and connecting all parts of the CHIPS Act along with existing innovation infrastructure.

- Technologies across the full stack, spanning from materials and devices through to the packaging and end-application, via interlocking multidisciplinary research.

- The full supply chain from materials through packaged and tested chips

- R&D on different time horizons of 3-5 years, 5-10 years, 10-15 years

This is a complex system with different requirements for different layers, nodes, and end markets.

Although there are many reasons to do this, the biggest needs for a super-sized institute combining Microelectronics and Advanced Packaging Technology are as follows:

- 1) Microelectronics and Advanced packaging Technology (MAPT) R&Ds need to be codeveloped to maximize performance, minimize cost, and meet the stringent requirements of future technology systems such as autonomous vehicles, energy-efficient AI, and highperformance data centers. Splitting them would lead to optimization of one at the performance cost of the other. Performance potential can only be achieved by keeping them together throughout the R&D phases and codeveloping technical solutions. The future of microelectronics will be integrating heterogeneous technologies in three dimensions which required close co-design and optimization throughout the applied research and the development processes.

- 2) Industry must collaborate to gain and maintain competitiveness. Splitting microelectronics and APT would lead to bifurcation of the industry partners because industry does not have the resources (membership dues and manpower) or risk-tolerance to join multiple institutes.

- a) Industry is getting co-investment fatigue with the many options of joining NSTC, NAPMP, USA Institutes, DOD Commons, etc.

- b) Industry must collaborate with each other to be more effective. If industry is split into different institutes, there will be no collective learnings and direction setting.

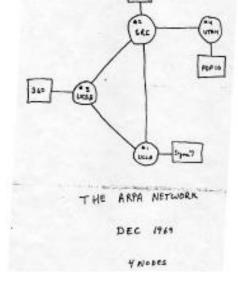

- 3) Universities need to collaborate with each other across topics and disciplines to maximize effectiveness. R&D is a team sport and more effective when working together, as evidenced by the DARPA/SRC's JUMP (Joint University Microelectronics Program) program

consisting of 6 university centers, having many universities supporting each research center and their corresponding six breakthrough challenges.

a) For example, DARPA's ARPANET program in 1969, which became the foundation of the modern internet, was formed through a collaboration with UCLA, UCSB, University of Utah, and SRI

Figure 12. An early 'napkin' drawing of the concept for an ARPANET, courtesy of DARPA

#### C) Advantages of a second, smaller Institute

A second institute of 'standard size' that performs R&D on the topics of Virtualization, Visualization, and Automation (VVA) would be highly valuable to supporting US manufacturing. Automation of MAPT manufacturing would help solve two problems and would be imperative in achieving the goals outlined in the CHIPS legislation.

- Automation could reduce the asymmetric advantage of manufacturing in lower-cost labor markets such as SE Asia. SE Asia has become a manufacturing hub for packaging because of the high manual labor needed for manufacturing coupled with the low cost of labor in the region. Lowering the labor intensity of packaging manufacturing could 'level the playing field' and make US manufacturing of packaging more competitive.

- 2. Automation of MAPT manufacturing could ease the semiconductor industry labor shortage by automating steps that are currently done manually, or that do not yet exist, and could be adopted with automation at its onset. Replacing these steps would lead to fewer employees needed per manufacturing site and thus minimize the labor shortage.

The VVA institute would have some strategic overlap with the MAPT institute on the edges of what is included for each, but they must work synchronously on technology development, technology transfer to manufacturing, and on EWD. Specifically, technology developed in one institute could add technology from the other and then transfer to a set of companies to achieve even greater impact.

#### D) Partnerships

Partnering with others is critical and was discussed extensively in the response to Question 6.

Specifically, the Super-Sized MAPT Institute must be designed from the beginning to partner with the creators/operators of the NSTC, NAPMP, DOD Commons, DOE R&D, and NSF programs. Ideas for collaboration include, but are not limited to:

- Ability to co-fund collaborative research projects

- MMI use of facilities and infrastructure created by NSTC, MAPMT, DOD Commons.

- Note it is our understanding that, due to NSTC, MAPMT, DOD Commons potentially having budgets ~5X larger than a \$250M/year manufacturing institute recommended in this paper, these adjacent programs should have a heavy emphasis on building innovation pipeline infrastructure including tools, equipment, and facilities that does not currently exist. MMI R&D projects, along with other programs' R&D projects, would be users of that infrastructure and should be fully integrated with those programs.

• Leadership of each of the NSCT, NAPMP, and MMI should participate in a Leadership Council which helps direct and coordinate the activities of each to make them cohesive.

**Q8.** What membership and participation structure for a Manufacturing USA semiconductor institute would be most effective for ensuring participation by industry, academia, and other critical stakeholders, particularly with respect to financial and intellectual property obligations, access, and licensing? Based on your knowledge of current Manufacturing USA institute practices, are the needs of potential semiconductor institutes different than for other institutes?

#### [Note: In addition to the response below, please reference the response to Question 6]

We support the current general Manufacturing USA tiered membership model with project and access rights based on membership level. However, we suggest additional 'blue stamp' access for Diversity, Equity, and Inclusion (DEI) organizations, and small businesses. We also suggest a means to ensure a longer-term commitment from 'gold' (highest)-tiered membership, for an additional 5 years for joint R&D projects. This commitment should include a requisite DEI for Education and Workforce Development (EWD) component.

Government should not fund specific R&D, workforce development and other programs in perpetuity, but rather should use seed funding that creates and builds an institute that can operate in perpetuity with industry as the primary funding source. Only if industry is the primary funding source will it be industry-aligned and industry-serving. An estimate is that government would continue to get value form the institute and would therefore desire to fund it. Looking at other similar models, 20- 30% of revenue for effective existing collaborations comes from government. IP rights, governance, revenue models, and operations should be structured similarly to other institutes and incorporate best practices that can be borrowed from them. A few key points:

- Must be industry-led, have government oversight, and strong academic partners and be highly inclusive of the broad ecosystem

- Inter-academic collaboration is important because of the high degree of technology required for success in the industry

- IP rights have to be balanced to allow industry members to profit from them while also recognizing the value creation by academia.

- IP models' balance must include different options, perhaps some IP will be made publicly available while other IP will offer a high-competitive advantage for

sponsoring member(s) and therefore should provide some terms of exclusivity or protection.

Manufacturing continues to add more advanced materials into the manufacturing process, including materials that can be reproduced but are not always well understood scientifically. Additionally, new materials need to be assessed for environmental health and safety which needs to be part of the research process.

The membership structure should be adaptable and flexible to encourage participation from all parts of the ecosystem, including industry (large and small business), defense, academia, government, trade organizations, and non-traditional participants. There should be a low barrier to entry for participation in the institute and should include meaningful incentives to attract members of special interests such as underrepresented minorities, woman, and veterans.

Membership should require a multi-year commitment but will have flexibility to allow members to shift from one type of membership to another. This will ensure that their membership category is aligned with their organization's needs and that they are maximizing the benefit from their organization.

Membership will be done on a Tiered basis with different costs and different rights/benefits:

| Tier   | Description                                                                 |  |

|--------|-----------------------------------------------------------------------------|--|

| Tier 1 | Large companies: manufacturing, fabless, equipment, materials, EDA, leading |  |

| Tier 2 | Mid-size companies, defense, participating academics                        |  |

| Tier 3 | Small companies, government labs, incubators, following academics, trade    |  |

International members aligned with US interests will not only be permitted but will be encouraged to join and participate. For example, TSMC, Samsung, NXP, TEL, and many others are leaders in the semiconductor field with facilities in the US. It is important to attract organizations like this to have a more complete membership profile with potential to perform even more manufacturing in the US. These will comply with existing and future regulatory requirements.

## Section 3: Strategies for Driving Co-Investment and Engagement

**Q9.** The authorizing statute for Manufacturing USA requires at least an equal non-federal coinvestment in Manufacturing USA institutes to match the federal investment. From your perspective, what are the most significant considerations to garner support for the required coinvestment for a Manufacturing USA semiconductor institute? What is the anticipated impact of the new Investment Tax Credit (ITC) for industry established in the CHIPS Act on the level of investment in the new Manufacturing USA semiconductor institute(s), in facilities, including for manufacturing equipment and construction? How might a Manufacturing USA semiconductor institute be set up to best leverage the Investment Tax Credit?

The semiconductor industry needs to be at the forefront of cutting-edge development and ideas, but economic pressures do not always allow them to invest in such endeavors. These hurdles are especially great for small business. A shared mission and goal with academia and government will help alleviate some of that burden while pushing technology forward for the good of the country. Government subsidies for research also allows industry to push into a higher risk tolerance that they cannot otherwise afford. Correspondingly, industry must see a direct path for returns of investments in an endeavor such as a Manufacturing USA Institute.

To maintain financial support from industry, the Institute's technical direction must be industry led with advisory support from academia and government. To attract and continue support for the required co-investment, industry must realize value from financially supporting the Institute. For that to happen, the work of the Institute must have **three important qualities**:

- Relevance The Manufacturing USA Institute must be relevant to the industry's needs by aligning with their current and future objectives. Corporations are under great economic pressure, so to invest in an institute, they need to justify the cost with the future potential value-add to their business. Industry, however, is not the only source of cost share. State, local, and regional governments should provide important, indirect cost share through regional support and public awareness. Similarly, their indirect contributions must be relevant to the objectives of economic development.

- 2) High Quality A Manufacturing USA Institute must be able to provide its members with the best researchers, facilities, and employees for the workforce. Rather than relying only on researchers in the top 5 research institutions, the Institute would ensure quality through diversity. By engaging future talent across a diverse community, the result will be more innovation, opinions, solutions, and ideas. The Institute needs to provide the venue to

bring together all aspiring best researchers to be mentored by the industry's seasoned professionals.

3) High Volume – With diversity in members comes diversity in interests. Therefore, the Institute must have a high enough volume of research covering a large breadth of topics to ensure all members see a critical mass and sufficient value to address their ever-evolving business needs.

These three factors can be achieved with tight integration between university, industry, and government to further ensure industry continues to financially support the institute. This alignment must be done at a scale relevant to industry and should ideally resemble SRC's Industry Liaison program. The Liaison Program is a powerful partnership that brings together university researchers, graduate students, and industry R&D experts to create profound impact. The Program's goals are:

- Develop Tomorrow's Workforce Create a positive experience for student researchers that leads to a career in the semiconductor/microelectronics-related field and helps to growth the semiconductor workforce talent pipeline in a diverse and inclusive way

- Align Research Relevance Maximize the research relevance to projected industry needs

- **Transfer Technology** Minimize the time required for the research results to make an impact on the semiconductor industry, and identify potential patents and insights that may benefit member companies

A second mechanism for achieving the three qualities list above is for the institute to create large academic research centers that provide maximum value to industry, academia, and government. Research centers such as Texas Analog Center of Excellence (TxACE)<sup>18</sup> are excellent examples of collaborative efforts among these three vectors.

The new Advanced Manufacturing Investment Credit enacted as part of the CHIPS and Science Act of 2022 ("CHIPS Act") is a vital complement to the semiconductor grant program also enacted as part of the CHIPS Act. These important federal incentives indirectly support additional funds for important semiconductor research and innovation that aligns well with the mission of the Institute.

<sup>&</sup>lt;sup>18</sup> https://txace.utdallas.edu/

**Q10.** For the required non-federal co-investment for a Manufacturing USA semiconductor institute, with respect to the different types of co-investments (e.g., cash, equipment donations, facilities access, etc.), are there factors unique to the semiconductor industry that would impact how the co-investment could be structured to best support the institute?

There are several factors that make the semiconductor industry unique as described in the response to Question 6. Two of these factors should be considered for how the co-investment could be structured.

The first factor is the high R&D intensity (R&D investment/revenue) of the industry, second only to the pharmaceutical industry (Figure 13). On average, 20% of a company's revenue is spent on R&D costs<sup>19</sup>. Because of this, the institute should allow co-investment contributions from industry to be in the form of internal R&D activities that support specific projects competitively selected by the institute to be performed by the company offering the co-investment. That is, if Company A is selected as a performer on a \$2M R&D project, some portion of the co-investment of that project could include work performed and paid for by Company A.

| Pharmaceuticals & Biotechnology           |              | <u>21.4%</u> |  |

|-------------------------------------------|--------------|--------------|--|

| Semiconductors                            | 18.0%        |              |  |

| Software & Computer Services              | <b>15.7%</b> |              |  |

| Real Estate Investment<br>& Services 9.2% |              |              |  |

| Mobile<br>Telecommunications 9.1%         |              |              |  |

| Media 8.4%                                |              |              |  |

| Technology Hardware<br>& Equipment 7.7%   |              |              |  |

| General<br>Retailers 6.8%                 |              |              |  |

| Alternative<br>Energy 6.2%                |              |              |  |

| Financial<br>Services 5.7%                |              |              |  |

Figure 13. R&D expenditures as a percentage of sales by industry

that own a small amount of equipment which requires them to outsource manufacturing tasks. As part of coinvestment contributions, foundries will be able to provide access to a variety of fab manufacturing facilities.

The second unique quality to the semiconductor industry is the high capital expenditure requirements to build and operate manufacturing fabrication, or 'fab' facilities. A compounding issue to the high capex for fabs is the decoupling in the industry between foundries that manufacture, and design companies

Design companies will contribute co-investment software, IP blocks, and design expertise to help R&D performers create better technology.

<sup>&</sup>lt;sup>19</sup> www.semiconductors.org/wp-content/uploads/2022/11/SIA\_State-of-Industry-Report\_2022.pdf

# **Q11.** What arrangements for co-investment proportions and types could help a Manufacturing USA semiconductor institute sustain operations in the absence of continued federal support?

The institute must be formed to align with industry's needs to be successful, and in doing so, industry, academia, and non-federal government will provide financial support as co-investment. Co-investment from the semiconductor industry for collaboratively funded R&D is already happening with leading companies in the industry currently contributing millions of dollars, independent of federal support, to collaborative R&D in such programs as those administrated by SRC. This model establishes that co-investment of R&D by industry can sustain operations in the absence of continued federal support.

The success of this model can be attributed to the fact that the collaborative R&D creates value for industry members and is aligned with industry needs. However, existing models for collaborative R&D in semiconductors is limited in size and scope by the R&D funds that industry can allocate to technology at this readiness and risk level. Typically, less than 10% of proposals submitted have sufficient collaborative industry funding to be selected for funding. With federal support, the collaborative R&D work needed to meet the NIST, and Manufacturing USA objectives listed in the RFI announcement could be met.

Co-investments for the institute will come in the form of cash from membership dues and from 'fee for services' while in-kind contributions will be made by universities, industry members, national labs, and others. A MAPT institute which includes the scope of microelectronics and advanced packaging technology together for a \$250M/year budget could achieve cost-matching of 1:1 at startup with the opportunity to growth throughout 5-year federally supported period.

**Q12.** A Manufacturing USA semiconductor institute should support domestic competitiveness. How should relationships with foreign entities be structured or constrained to support domestic manufacturing priorities while maximizing the opportunities to leverage international expertise and resources? In what circumstances should the Manufacturing USA Semiconductor institutes and NIST as the federal sponsor, consider membership requests from foreign-owned businesses?

As the semiconductor industry fractured into manufacturing specialties such as Chemicals & Materials, Design, Fabrication, Packaging and Test, geographic regions emerged as hubs of the supply chain. This regional specialization has enabled global economic growth for over 40 years and the continuation of Moore's Law well beyond what a single actor, alliance, or region could accomplish alone. Although this regional growth enabled global economic prosperity, it has

resulted in a growing economic interdependence across regions, and therefore, supply chain fragility and national security risks.

To minimize this risk, the US needs to partner with foreign companies that manufacture in the US as well as companies that provide services that support US manufacturing. Accordingly, these types of companies should be welcomed and encouraged to participate in the Manufacturing USA Institute as they are important contributors to NIST's objectives. Examples of foreign companies that employ many domestic industry personnel and support US manufacturing include: NXP, Samsung, TEL, SK Hynix, MediaTek, TSMC, ASM, Siemens, and ARM. The institute should welcome and encourage participation from these and other companies.

The criteria for allowing foreign companies to participate in the institute should be that they:

- 1) Support US manufacturing while having some presence in the US

- 2) Do not have headquarters or majority ownership in nations of concern (China, Iran, Russia, North Korea, etc.)

- 3) Comply with existing and future international trade laws including ITAR, EAR, etc. Publications by The Department of Commerce's Bureau of Industry and Security should be used as a guide for determining admittance of companies with foreign headquarters.

**Q13.** How should a new Manufacturing USA semiconductor institute engage other existing Manufacturing USA institutes (https://www.manufacturingusa.com/institutes), including those awarded funds for work related to semiconductor manufacturing, and other manufacturing related programs and networks such as the Manufacturing Extension Partnership (https://www.nist.gov/mep) and the U.S. Department of Energy's Next Generation Power Electronics National Manufacturing Innovation Institute ("Power America")?

There are several ways for a new Institute to engage other existing Manufacturing USA Institutes. A great starting place would be for the Institute to share both operational and intellectual property models. Sharing best practices with other Institutes could be key to quickly and successfully launching and then operating the Institute before and after government funding. Leveraging knowledge among Institutes is a very low cost and high benefit activity.

Institutes should also share facilities and resources where applicable. The semiconductor industry has advanced manufacturing capabilities that could be made available to other Institutes. We also recommend that some of the new dollars that go to existing manufacturing institutes be dedicated to collaborative R&D projects between the MAPT MMUSAI and other institutes.

Joint R&D and workforce development projects should be approached together. This new Institute would share common interests with Power America, AIM Photonics, NextFlex, CESMII, and possibly other existing Institutes. By pooling funds from different Institutes, additional leverage can be obtained to make R&D dollars even more impactful. Additionally, bringing together Institutes that have similar interests, but different viewpoints and motivators, would result in more robust innovation.

# **Q14.** How should a Manufacturing USA semiconductor institute interact with State and local economic development entities?

The Institute should leverage resources from across the United States, which will also help regional development throughout the country, especially in regions that do not currently participate in or support semiconductor manufacturing. The central region of the US has excellent resources and talent that could contribute to the mission of the Institute if a working relationship could be developed with State and local economic entities. These states have many universities, national labs, and research professionals that could further contribute to both the industry and the Institute's mission. State and local economic entities could assist in furthering workforce development efforts to the benefit of all. An example of this is the state investments with IEDC (Indiana Commerce) in recent years, and the corresponding growth in Indiana with TSMC, Skywater, and MediaTek.

In the past few years, various companies have set up new fabs across the US. Intel announced a new \$20 billion factory outside Columbus, Ohio that will also create 7,000 construction jobs and another 3,000 permanent jobs. Samsung set up a \$17 billion factory in Texas. Also in Texas, Texas Instruments invested up to \$30 billion in a new chips foundry, and Global Foundries set up a new chips factory in New York state. Wolfspeed-Cree spent \$1 billion to expand a current plant in North Carolina, SK Group invested in a new U.S. R&D center, and Micron is expanding US production in NY and Idaho. However, each region has its own DEI challenges. A supersize Institute will be able to work with each regional area to develop an equitable workforce plan.

**Q15.** How should a Manufacturing USA semiconductor institute coordinate with and inform standards development bodies on the need to modify existing or develop new standards as a result of this initiative?